SPI

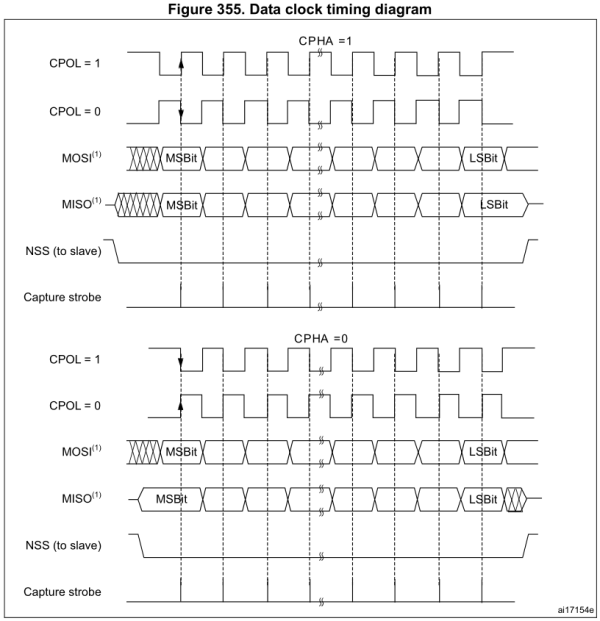

クロックの論理とタイミングを組み合わせることで,4つのパターンに分類できる.

通信する相手によって合わせる必要がある.

| Mode | POL | PHA |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 0 | 0 |

| 2 | 1 | 1 |

| 3 | 1 | 1 |

クロックの論理(POL)

正論理であれば0,負論理であれば1

クロックのタイミング(PHA)

1つ目(ラッチ先行)であれば0,2つ目(シフト先行)であれば1

stm32F3xxリファレンスマニュアルより

マルチスレーブ

それぞれのスレーブのCSを制御することでマルチスレーブを構成.

ものによってはディジーチェーン接続に寄って信号線の本数を減らせる.

しかしディジーチェーンはすべてのSPIスレーブデバイスが対応してるわけではない.