ZYBO

販売しているDigilentのページ → Zybo

予めVivadoのインストールをやっておく.

Board file

手動でBoard fileを追加しなくても,自動的に登録されたリポジトリからダウンロードできるようになっていた.

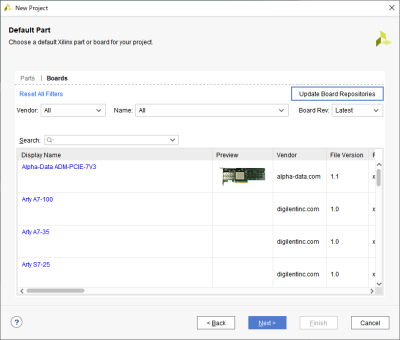

Vivadoでプロジェクトを作成する際に以下のような画面が出るので,「Update Board Repositories」をクリックし,確認画面で「Download」をクリックすると,登録されているリポジトリからBoard fileをダウンロードしてきてくれる.ここから自分が使用するボードを選択すれば良い.

購入可能なボードは基本的に登録されている.自分で基板起こしたり,Xilinxのリポジトリに登録されていないボードについては自分で追加する必要がある.

アリエクで流れているようなボードは流石に登録されていないだろう.

XilinxのGitHubリポジトリXilinxBoardStore/Digilentにある.

Board fileを入れる.

Vivado Version 2015.1 and Later Board File Installation (Legacy)

に従いファイルをペーストする.今回の場合.

E:\Xilinx\Vivado\2019.1\data\boards\board_files 内部にzyboフォルダをペーストした.

File → Project → New でプロジェクトを新規作成.

LEDは13 Basic I/Oによると以下の通り

| LEDs | Pin |

|---|---|

| LD3 | D18 |

| LD2 | G14 |

| LD1 | M15 |

| LD0 | M14 |

クロックソースはいくつかあるが,125MHzの基準クロックがL16に直接接続されている.これはPSのクロックと完全に独立している.

12 Clock Sources

VitisでApplication Projectを作成する.

Vitis + Vivado + zynq = 楽しい

この記事が画像つきで一通りなぞっててわかりやすい.

もともとZyboの勉強にはZYBO (Zynq) 初心者ガイド (2) Hello Worldプロジェクトを大変参考にしていた.しかしソフトウェア開発環境がVItisになったという経緯.

Platfom ProjectよりFreeRTOSドメインを追加してビルドしたらFreeRTOSを動かしたApplication Projectも作成してテンプレートプロジェクトを起動できた.

喜んでいたかとあとから公式の資料で見つけた.

クイック スタート

lwIPでEcho Server

VitisのテンプレートプロジェクトからEthernetを使ったEchoServerの構築.

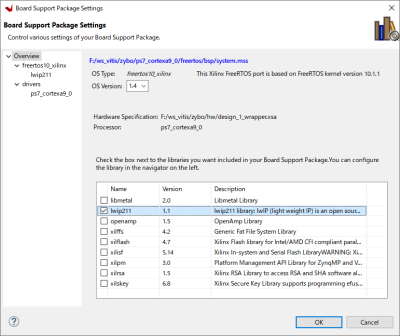

PlatformでlwIPライブラリを追加する

Platformプロジェクトの設定(プロジェクト名.spr)→ Board Support Package → Modify BSP Settings…

から「lwip」ライブラリにチェックを入れる☑(画像では「lwip211」となっている)

ベアメタルの場合はこれだけでいいが,freertos上で動かす場合はもう1つ設定が必要.

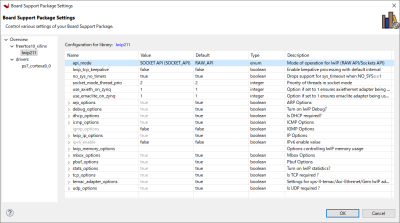

左型のタブから,画面を「lwip211」に切り替える.

lwip211の設定画面になるので,api_modeの部分をSOCKET_APIに切り替える.(デフォルトはRAW_APIとなっている)

これで,ソースコード内のLWIP_SOCKETが1になる.

この設定が適用されていないと,そもそもアプリケーションプロジェクトでEchoServerを選択することができない.

このサンプルは複数の接続を確立できる.なので1つのZYNQに対してTeraTermで複数個立ち上げて全部接続しても,それぞれに対してエコーバックしてくれる.

また,IPをあわせていれば同じネットワーク内の別PCからもアクセス可能.ネットワークの仕組み考えたら当然といえば当然だけど,lwipのエコーサーバのサンプルだけでここまでやれるのはよい.

error: lwip/sockets.h: No such file or directory

Xilinx Vitis学习教程:ZYNQ之lwip使用Echo server(2)